# Implementation of Faster-than-Nyquist signaling transceivers

#### Deepak Dasalukunte Fredrik Rusek, John. B Anderson, and Viktor Öwall

Circuits and Systems group and Center for High Speed Wireless Communication

Lund University, Sweden

### Outline

- Motivation for Faster-than-Nyquist signaling (FTN).

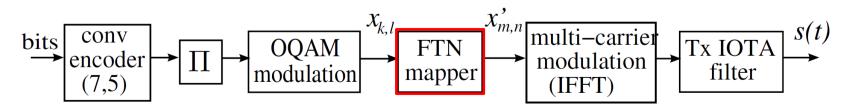

- FTN Transceiver for multi-carrier systems.

- Decoding performance.

- Hardware considerations for FTN decoder implementation.

- Results

- Performance of FTN decoder from RTL simulations.

- Area usage.

- Power and throughput.

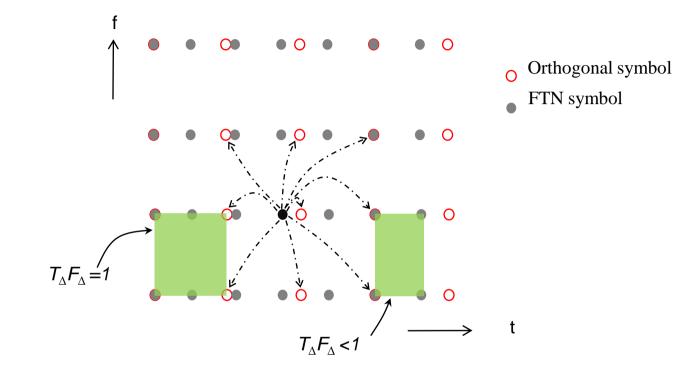

- Original concept by J.E. Mazo in 1975 (Bell Syst. Tech. J).

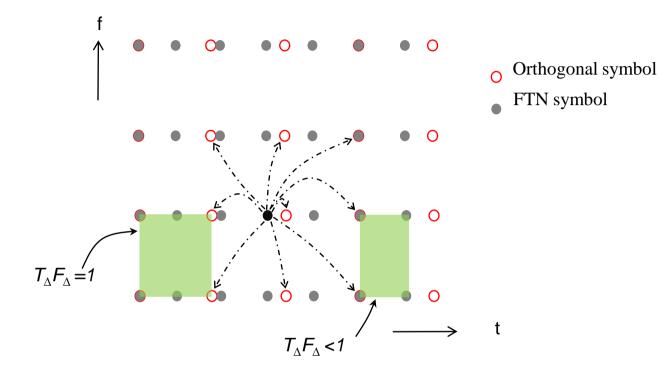

- Main idea

- to transmit information beyond that allowed by Nyquist's criterion for ISI free transmission.

- more symbols stacked in time and/or freq induce intentional interference.

- Bandwidth efficient systems.

## Motivation

- Bandwidth is a premium resource today.

- Improving logic density with advancing silicon technology.

- more complex signal processing in transceivers and use bandwidth resources efficiently.

- Principal objective :

- Feasibility evaluation and hardware implementation of decoders for FTN.

- Multicarrier systems (OFDM based).

- Tradeoff between complexity overhead vs. improvement in bandwidth efficiency

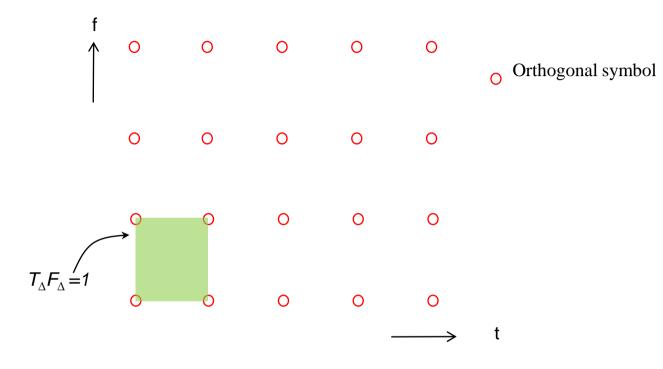

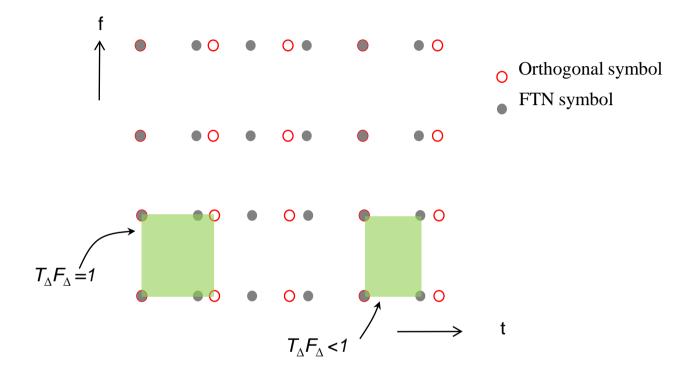

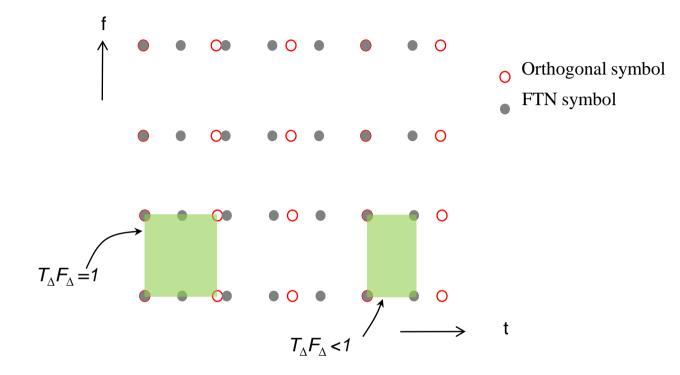

### FTN vs. Orthogonal system

### FTN vs. Orthogonal system

### FTN vs. Orthogonal system

### FTN vs. Orthogonal system

### FTN vs. Orthogonal system

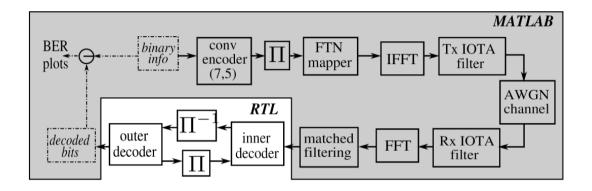

FTN transmitter: look-up table based

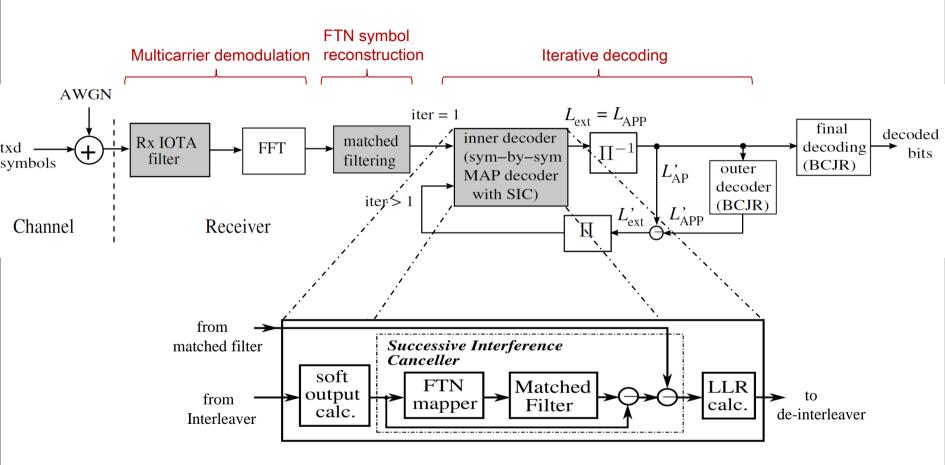

#### Receiver

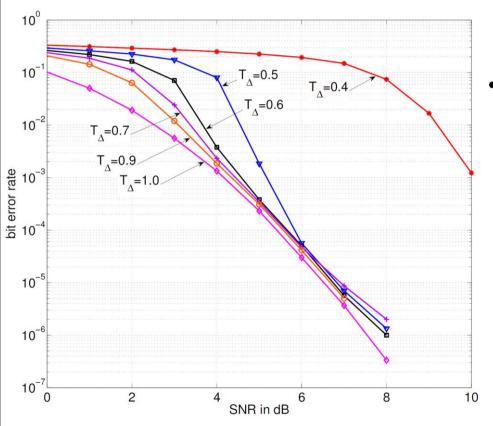

## **Results: Receiver performance**

LUND UNIVERSITY

• 2.5x improvement for the given system

### **Fixed wordlength evaluation**

- Transceiver model used to determine

- wordlengths

- 4, 6, 8 and 10 bits evaluated.

- 8 bits minimum required.

- no. of iterations : 8.

- Block size: 2016 symbols.

- 3GPP interleaver.

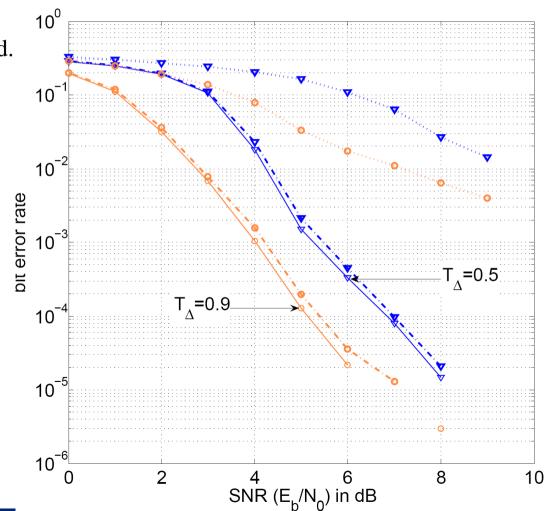

### **Evaluating the implemented design**

- Some degradation in RTL performance:

- more averaging required.

- 6 bit wordlength for outer decoder.

- internal underflows.

- Consistent with simulation model.

### Results: pre-optimization.

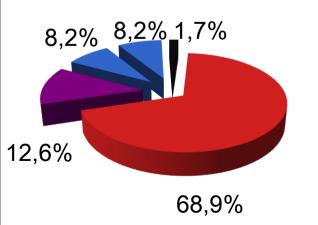

- Chip area : **0.519 mm<sup>2</sup>** (~250k gate count ST 65nm standard cell CMOS)

- 0.158mm<sup>2</sup> logic and 0.360 mm<sup>2</sup> memory (~17kB).

- 64% of memory in Inner decoder.

- Estimated Power: **44mW** (80% in the memories)

- Speed and throughput: **3.2Mbps** at **300MHz**.

- Inner Decoder

- Outer Decoder

- Interleaver

- De-Interleaver

- Global FSM

### Conclusion

- A simulation model of the complete FTN transceiver realized.

- to evaluate the performance.

- explore design space for hardware implementation.

- Hardware architecture for the FTN system.

- Implemented in 65nm CMOS (tapeout Nov!).

- Complexity overhead.

- Memory : same order as a simple max-log-MAP implementation ((7,5) conv code).

- Logic: ~5 times (time multiplexed resources: matched filter, FTN mapper)

- Higher bandwidth efficiency through FTN in practice.

## Thank you!