# Introduction

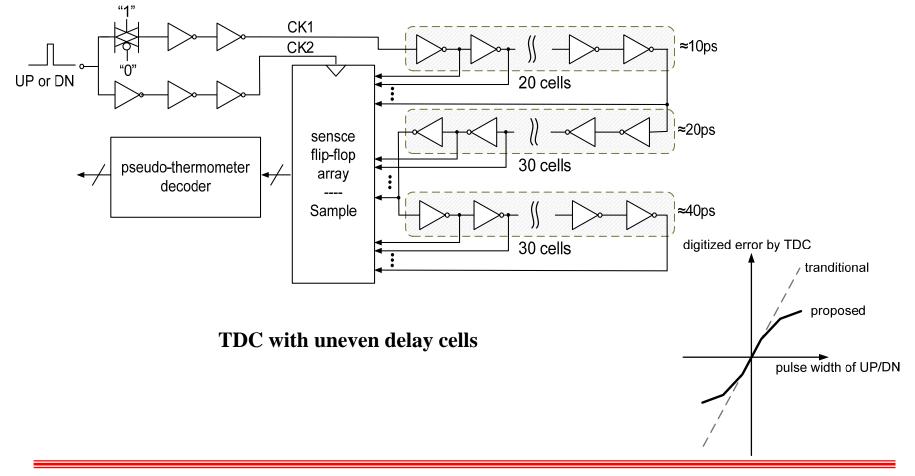

$\succ$  Good quantization noise requires a small unit delay time in TDC line. A large number of cells of TDC are required considering an wide cover range (period of reference clock).

> Only a small number of TDC cells will be used when the loop (structure.1) is in the locked state. The rest of the cells are used only at acquisition. The shortest-delay cells, resulting in the highest time resolution, are used only in the first part.

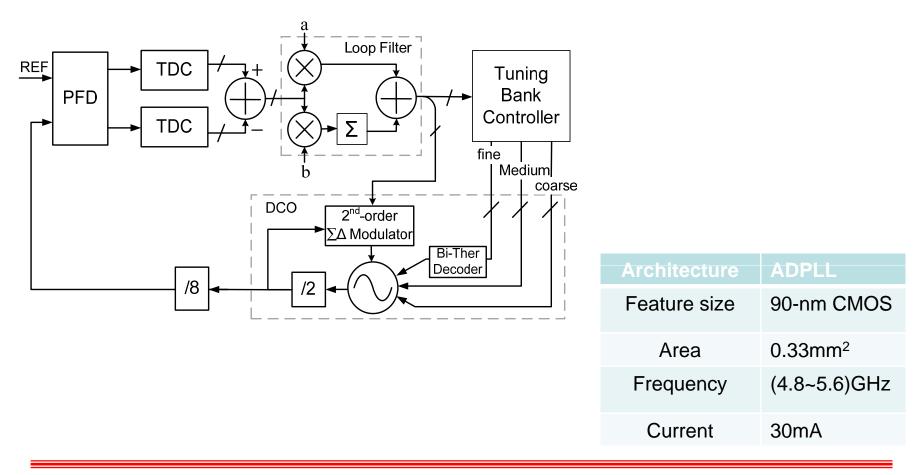

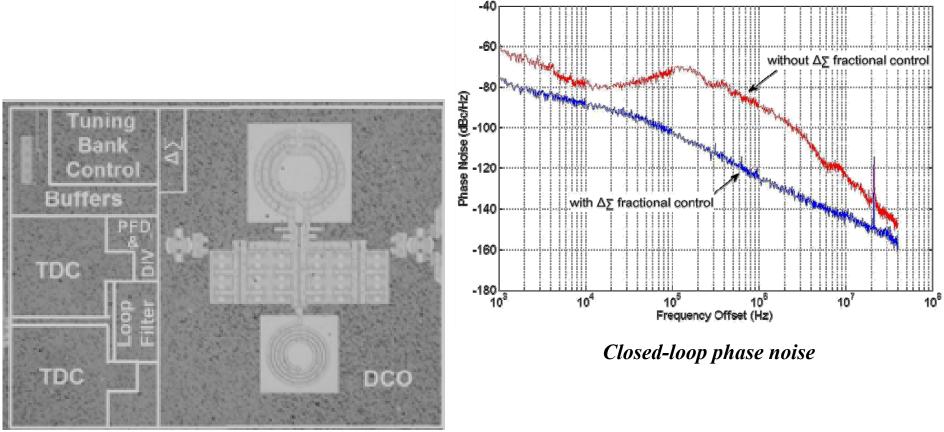

> A 5GHz ADPLL based on the uneven-cell TDC is implemented using 90-nm CMOS.

Loop Architecuture

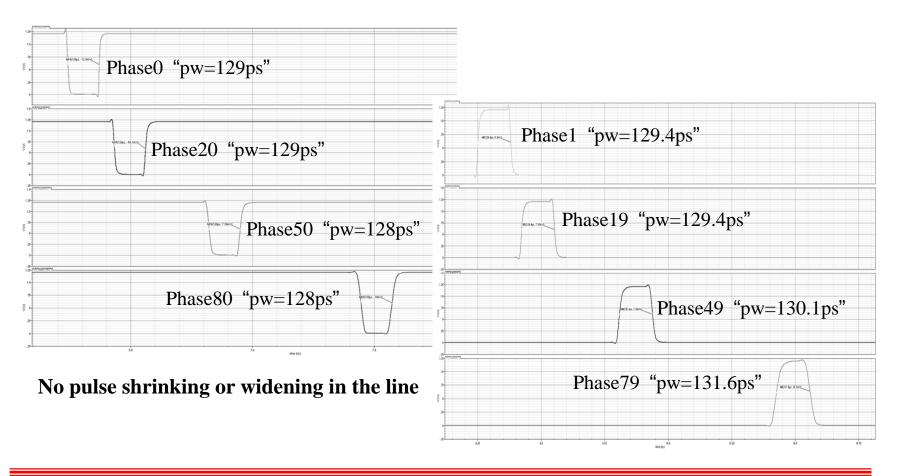

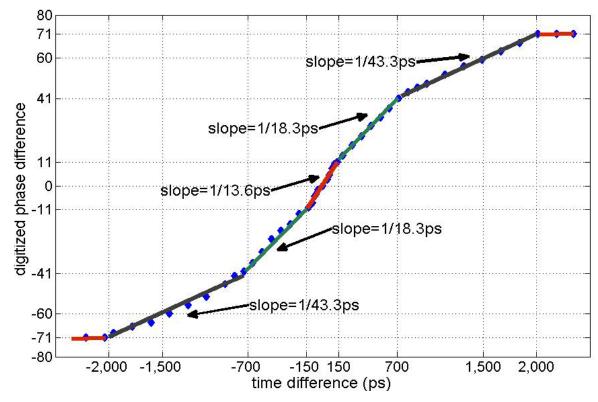

Uneven-Delay-Cell Time to Digital Converter

Uneven-Delay-Cell Time to Digital Converter

Uneven-Delay-Cell Time to Digital Converter

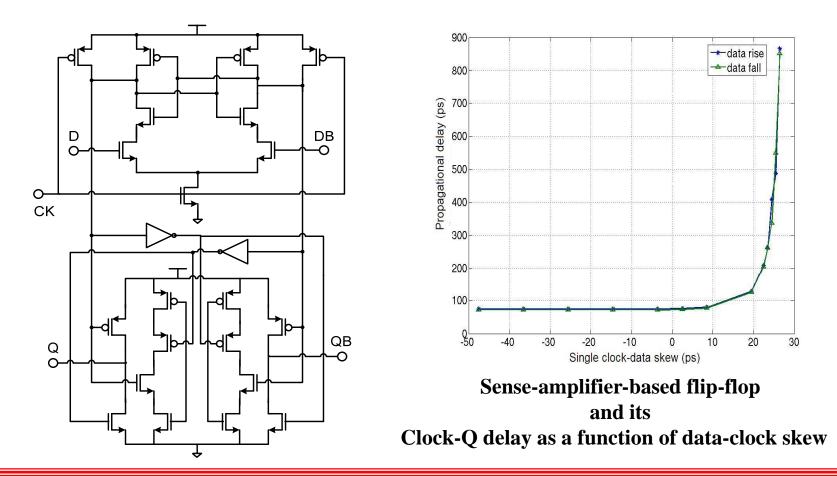

TSPC Phase and Frequency Detector

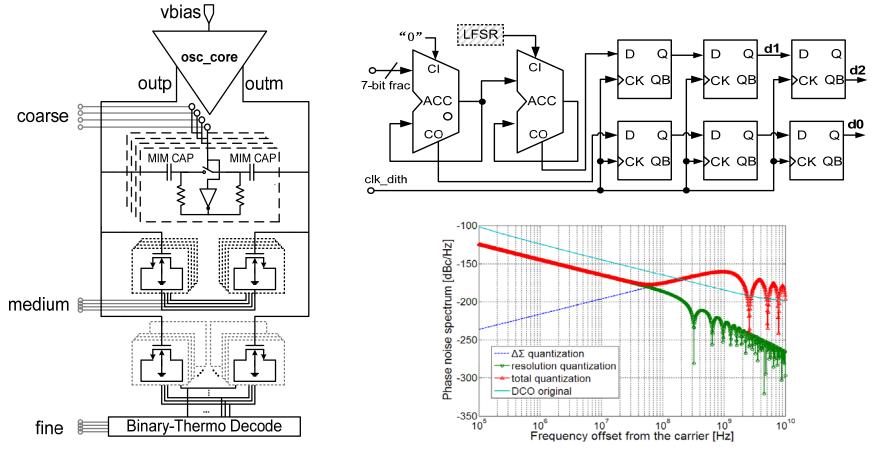

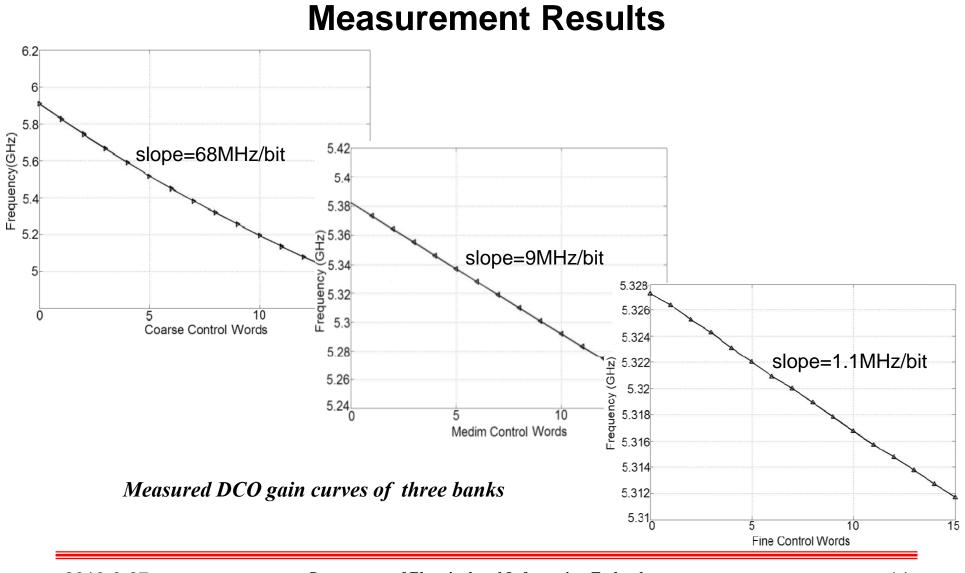

Digitally-Controlled Oscillator with Sigma-Delta Fractional Modulator

#### **Circuit Description** in\_sign Digital Loop Filter κ=0 & Υ:0∹ а X=1 & Y:1-> 1/16 out sigr **∕**►frac $H_{close} = \frac{K_{TDC}K_{DCO} \cdot a \cdot s + K_{TDC}K_{DCO} \cdot b \cdot f_{REF}}{s^2 + K_{TDC}K_{DCO} \cdot a \cdot s / N + K_{TDC}K_{DCO} \cdot b \cdot f_{REF} / N}$ clamp extremun 01111...1 or Σ 10000...0 fref/s overflow & underflow control $H_{TDC,noise} = \frac{(a \cdot s + b \cdot f_{ref})K_{DCO}}{s^2 + K_{TDC}K_{DCO} \cdot a \cdot s / N + K_{TDC}K_{DCO} \cdot b \cdot f_{ref} / N}$ $s^2$ $H_{DCO,noise} = \frac{1}{s^2 + K_{TDC} K_{DCO} \cdot a \cdot s / N + K_{TDC} K_{DCO} \cdot b \cdot f_{ref} / N}$ -80 -95 +type-l +type-l -125 -200 10<sup>2</sup> 10<sup>6</sup> Frequency Offset (Hz) 10<sup>8</sup> 10<sup>10</sup> 10<sup>4</sup> 10 0 5 15 Frequency Offset (Hz) x 10<sup>5</sup> log x-axis linear x-axis

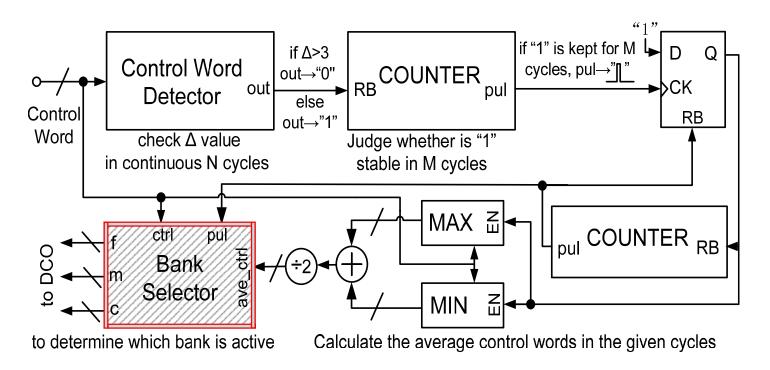

Tuning Bank Controller

Measured characteristic of Uneven-cell TDC

|                                  | [17]  | [6]     | [9]  | [18]  | This Work |

|----------------------------------|-------|---------|------|-------|-----------|

| <b>Technology (nm)</b>           | 65    | 130     | 130  | 130   | 90        |

| <b>Reference Frequency (MHz)</b> | 25    | 50      | 26   | 185.5 | 322       |

| Carrier (GHz)                    | 3     | 3.67    | 3.6  | 2.2   | 5.16/2    |

| Phase Noise (dBc/Hz@400kHz)      | -101  | -108    | -117 | -100  | -115      |

| Phase Noise (dBc/Hz @20MHz)      | NA    | -150    | -152 | NA    | -152      |

| <b>Power Consumption</b>         | <10mW | 46.7 mW | 40mA | 14 mW | 36mW      |

| Active Area (mm <sup>2</sup> )   | 0.4   | 0.95    | 0.86 | 0.7   | 0.33      |

Performance comparison

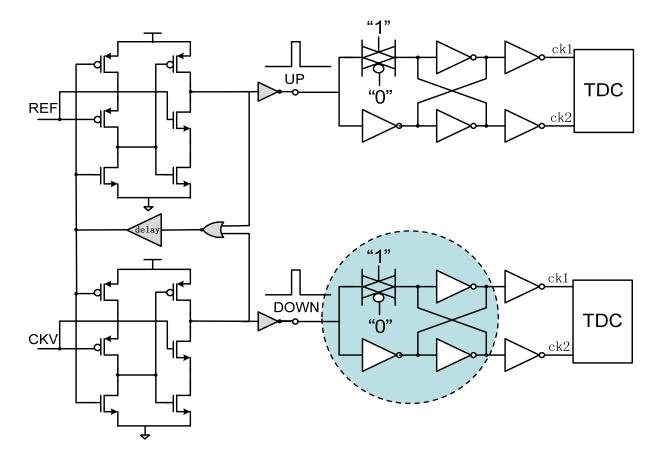

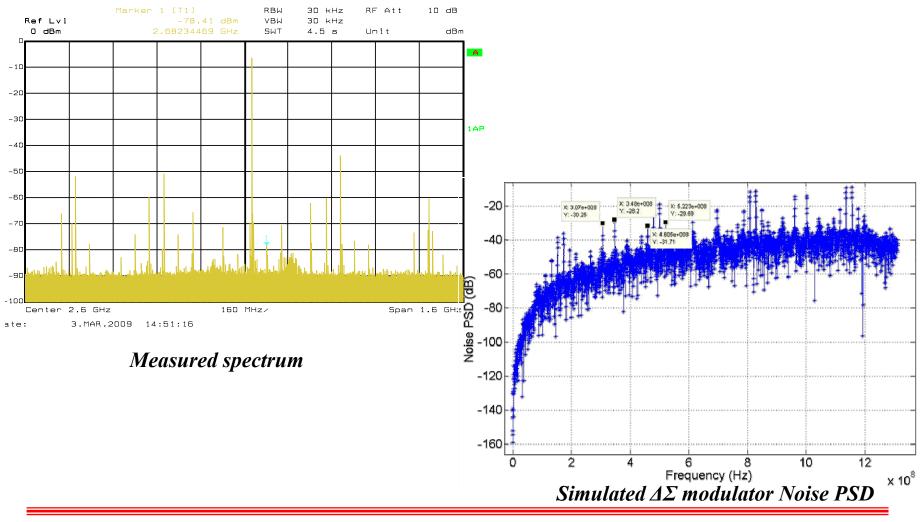

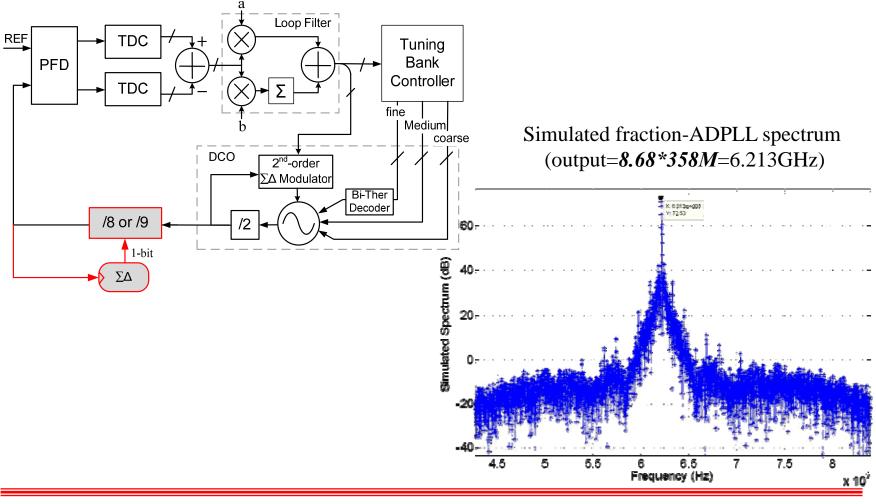

### **Fractional-N ADPLL modification**

# Conclusion

> An uneven-cell TDC based all-digital PLL is designed to reduce the design complexity without sacrificing phase noise performance.

$\succ$  The loop works self-adaptively thanks to an automatic tuning bank controller which tunes three DCO tuning banks one by one.

> A 1-bit truncation in the loop filter makes the ADPLL achieve a type-I noise characteristic, and track the reference like a type-II PLL.

$\succ$  The work can also be improved to be a fraction-N ADPLL using a fractional divider.