## A 26GHz 22.2dBm Variable Gain Power Amplifier

in 28nm FD-SOI CMOS for 5G Antenna Arrays

CHRISTIAN ELGAARD ANDREAS AXHOLT ERIC WESTESSON HENRIK SJÖLAND

ERICSSON & EIT LUND UNIVERSITY ERICSSON (ACCONEER) ERICSSON ERICSSON & EIT LUND UNIVERSITY

## **Presentation Outline**

- Motivation and Scope

- Architecture

- Design

- Simulation and measurement results

- Conclusions

## Motivation and Scope

- Targeting 5G mmW base station

- Large antenna array

- High integration

- Not possible with external PAs

- Many trancievers per chip

- Including digital baseband

- State of the art CMOS

## Motivation and Scope

- 5G mmW PA for Antenna Array System (AAS)

- High output power

- » For coverage at mmW

- 28 nm FD-SOI CMOS process

- High Power Added Efficiency (PAE)

- 10-year reliability

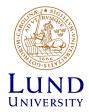

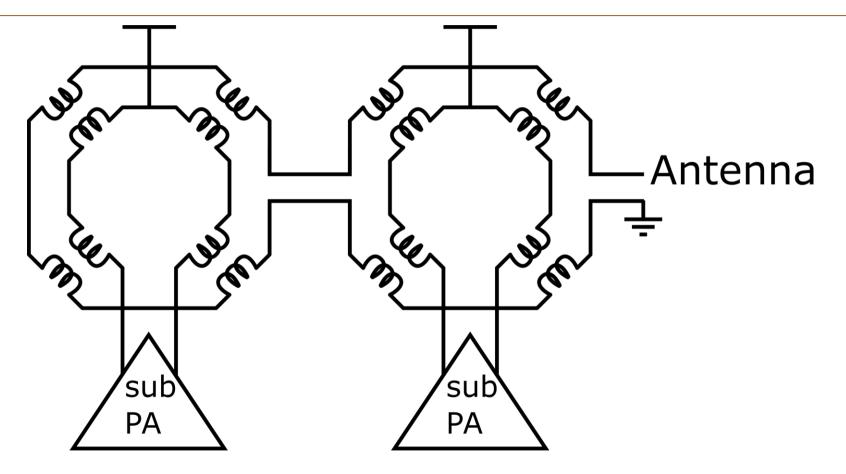

## PA Architecture –Part of a fully integrated transmitter

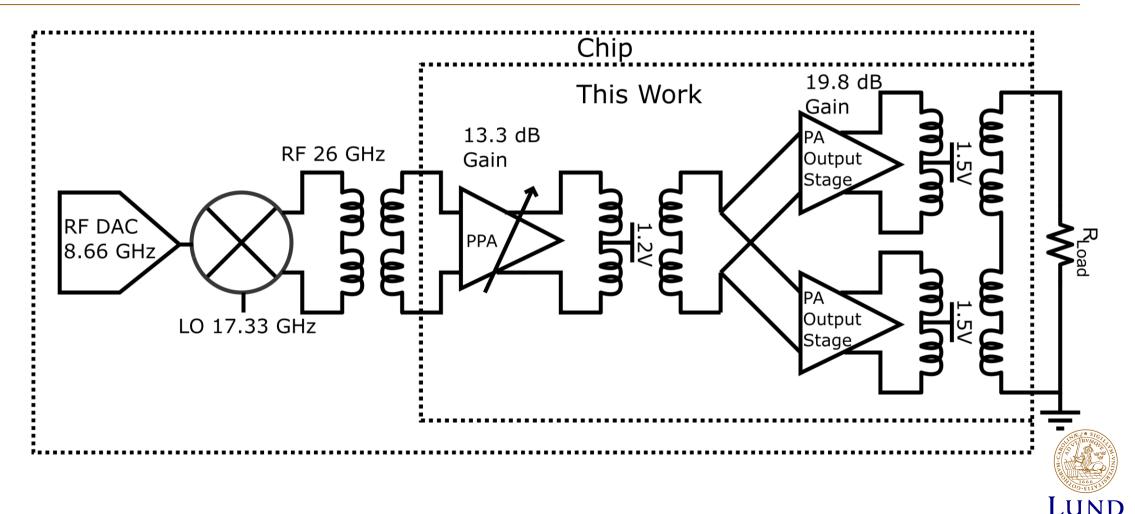

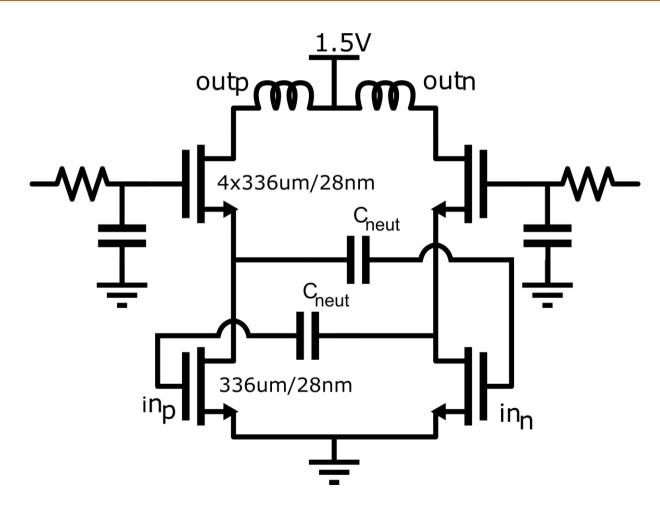

## PPA Design

## Sub-PA Design

## Output Combiner Design

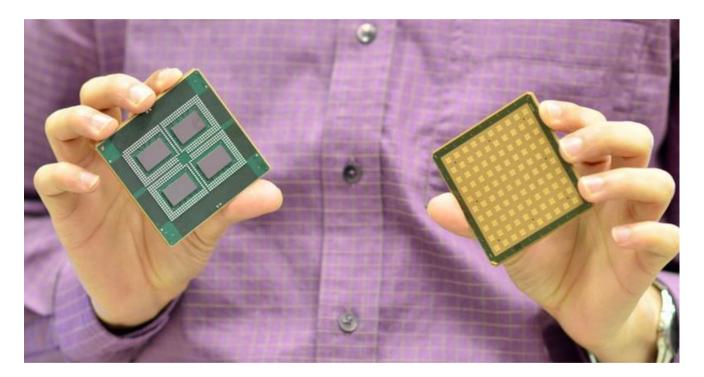

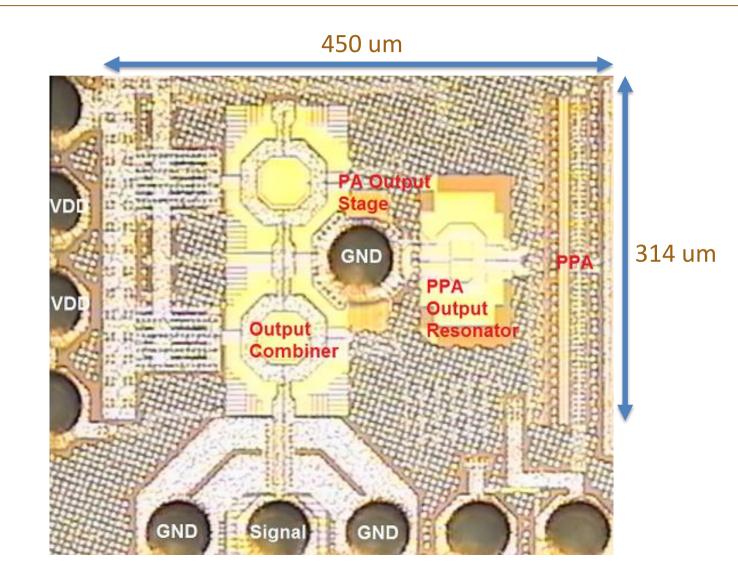

## Chip Photo

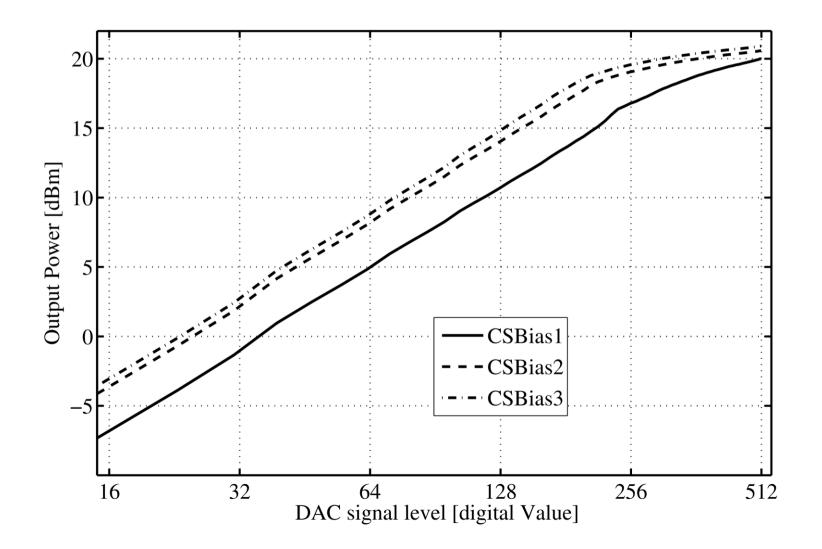

#### Pout vs DAC value

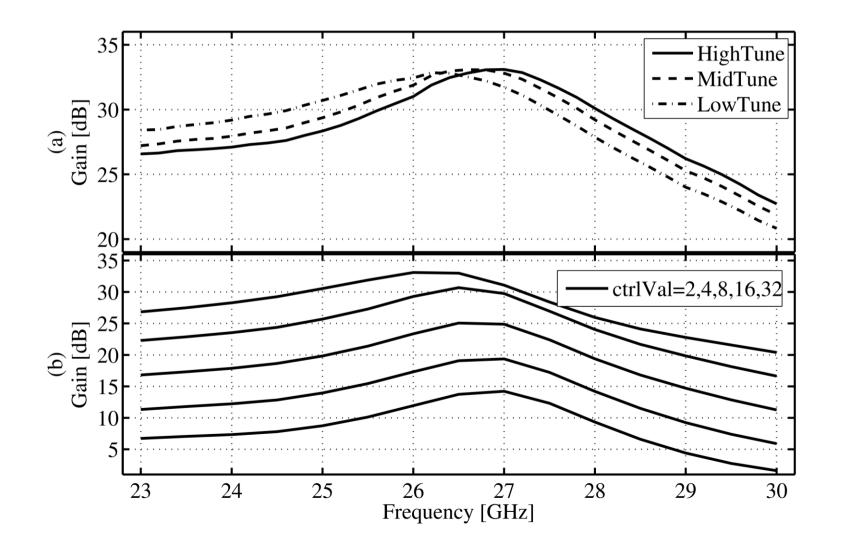

## Small Signal Measurement

| Parameter       | This         |              | RFIC'17 | RFIC'17 | ISSC    | ISSCC'16 |         | 5'16 |

|-----------------|--------------|--------------|---------|---------|---------|----------|---------|------|

|                 | Work         |              | [3]     | [4]     | [5]     |          | [6]     |      |

| Tech. [nm]      | 28 SOI       |              | 28 Bulk | 28 Bulk | 28 Bulk |          | 28 Bulk |      |

|                 | CM           | IOS          | CMOS    | CMOS    | CMOS    |          | CMOS    |      |

| Freq. [GHz]     | 2            | 6            | 27      | 32      | 30      |          | 28      |      |

| Pwr.Comb.       |              | 2            | 2       | 2       | -       | 1        | 1       |      |

| Gain Control    | 5 bits,      | 19dB         | None    | None    | No      | one      | None    |      |

| No. of Stages   | 2            |              | 2       | 2       | 2       |          | 1       |      |

| Vdd [V]         | 1.5          | 1.8          | 1       | 1       | 1       | 1.15     | 1.1     | 2.2  |

| $P_{sat}$ [dBm] | 20.6         | 22.2         | 18.1    | 19.8    | 14      | 15.3     | 14.8    | 19.8 |

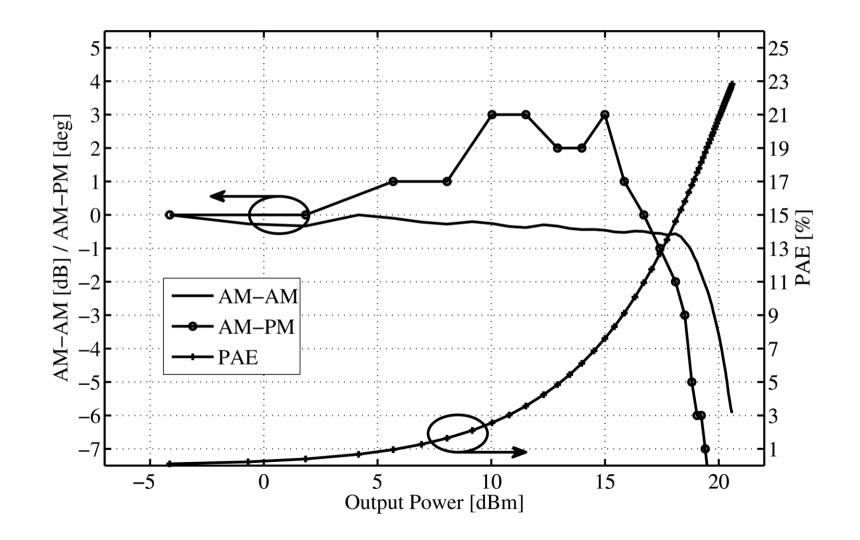

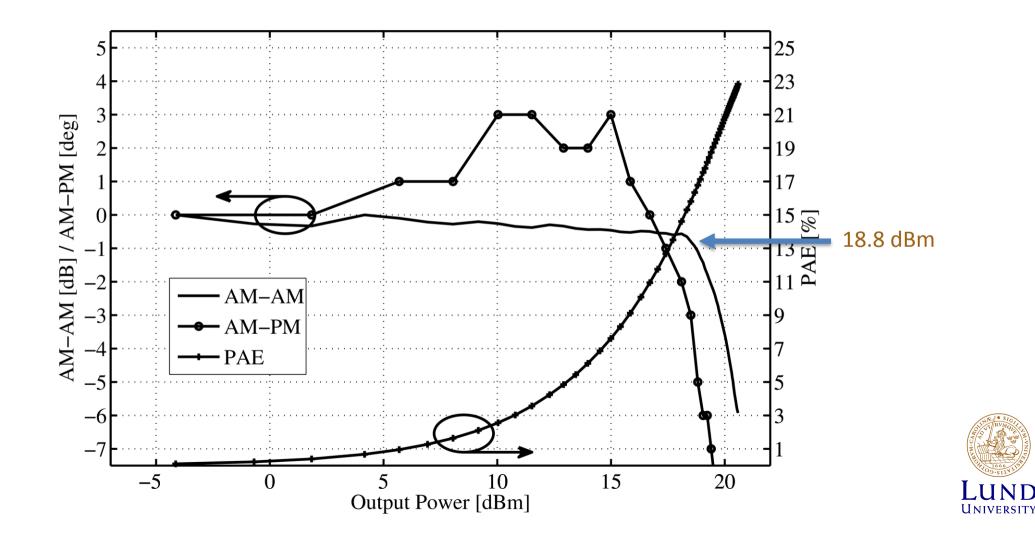

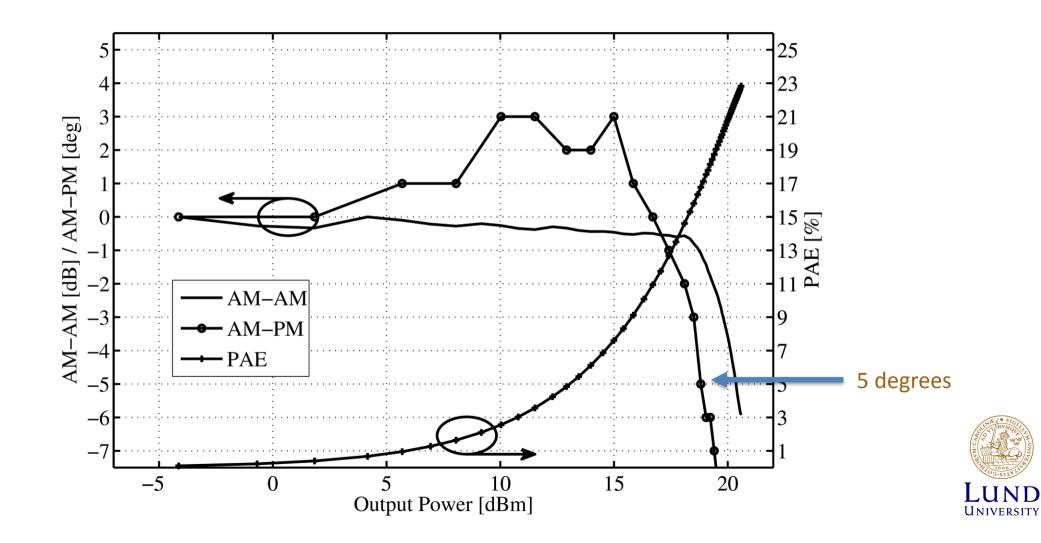

| $P_{1dB}$ [dBm] | 18.8         | 20.7         | 16.8    | 16      | 13.2    | 14.3     | 14.0    | 18.6 |

| $PAE_{max}$ [%] | $22.6^{(1)}$ | $21.3^{(1)}$ | 41.5    | 21      | 35.5    | 36.6     | 36.5    | 43.3 |

| $PAE_{1dB}$ [%] | $16.6^{(1)}$ | $14.6^{(1)}$ | 37.6    | 12.8    | 34.3    | 35.8     | 35.2    | 41.4 |

| $PAE_{max}$ [%] | $20^{(2)}$   | $19.6^{(2)}$ | 41.5    | 21      | 35.5    | 36.6     | 36.5    | 43.3 |

| $PAE_{1dB}$ [%] | $14.5^{(2)}$ | $13.5^{(2)}$ | 37.6    | 12.8    | 34.3    | 35.8     | 35.2    | 41.4 |

| Gain [dB]       | $33.1^{(3)}$ | $33.9^{(3)}$ | 20.5    | 22      | 15.7    | 16.3     | 10.0    | 13.6 |

| Area $[mm^2]$   | 0.144        |              | 0.361   | 0.59    | 0.16    |          | 0.28    |      |

<sup>(1)</sup>Not including PPA power consumption.

<sup>(2)</sup>Including PPA power consumption.

| Parameter       | This         |              | RFIC'17 | RFIC'17 | ISSC    | ISSCC'16 |         | 5'16 |

|-----------------|--------------|--------------|---------|---------|---------|----------|---------|------|

|                 | Work         |              | [3]     | [4]     | [5]     |          | [6]     |      |

| Tech. [nm]      | 28           | SOI          | 28 Bulk | 28 Bulk | 28 Bulk |          | 28 Bulk |      |

|                 | CM           | IOS          | CMOS    | CMOS    | CMOS    |          | CMOS    |      |

| Freq. [GHz]     | 2            | 6            | 27      | 32      | 30      |          | 28      |      |

| Pwr.Comb.       |              | 2            | 2       | 2       | ] ]     | 1        | 1       |      |

| Gain Control    | 5 bits,      | 19dB         | None    | None    | None    |          | None    |      |

| No. of Stages   | 2            |              | 2       | 2       | 2       |          | -       | 1    |

| Vdd [V]         | 1.5          | 1.8          | 1       | 1       | 1       | 1.15     | 1.1     | 2.2  |

| $P_{sat}$ [dBm] | 20.6         | 22.2         | 18.1    | 19.8    | 14      | 15.3     | 14.8    | 19.8 |

| $P_{1dB}$ [dBm] | 18.8         | 20.7         | 16.8    | 16      | 13.2    | 14.3     | 14.0    | 18.6 |

| $PAE_{max}$ [%] | $22.6^{(1)}$ | $21.3^{(1)}$ | 41.5    | 21      | 35.5    | 36.6     | 36.5    | 43.3 |

| $PAE_{1dB}$ [%] | $16.6^{(1)}$ | $14.6^{(1)}$ | 37.6    | 12.8    | 34.3    | 35.8     | 35.2    | 41.4 |

| $PAE_{max}$ [%] | $20^{(2)}$   | $19.6^{(2)}$ | 41.5    | 21      | 35.5    | 36.6     | 36.5    | 43.3 |

| $PAE_{1dB}$ [%] | $14.5^{(2)}$ | $13.5^{(2)}$ | 37.6    | 12.8    | 34.3    | 35.8     | 35.2    | 41.4 |

| Gain [dB]       | $33.1^{(3)}$ | $33.9^{(3)}$ | 20.5    | 22      | 15.7    | 16.3     | 10.0    | 13.6 |

| Area $[mm^2]$   | 0.144        |              | 0.361   | 0.59    | 0.16    |          | 0.28    |      |

$^{(1)}$ Not including PPA power consumption.

<sup>(2)</sup>Including PPA power consumption.

| Parameter       | This         |              | RFIC'17 | RFIC'17 | ISSC    | ISSCC'16 |         | S'16 |

|-----------------|--------------|--------------|---------|---------|---------|----------|---------|------|

|                 | Work         |              | [3]     | [4]     | [5]     |          | [6]     |      |

| Tech. [nm]      | 28 SOI       |              | 28 Bulk | 28 Bulk | 28 Bulk |          | 28 Bulk |      |

|                 | CM           | <b>IOS</b>   | CMOS    | CMOS    | CMOS    |          | CMOS    |      |

| Freq. [GHz]     | 2            | 6            | 27      | 32      | 30      |          | 28      |      |

| Pwr.Comb.       |              | 2            | 2       | 2       | ]       | 1        | 1       |      |

| Gain Control    | 5 bits,      | 19dB         | None    | None    | No      | one      | None    |      |

| No. of Stages   | 2            |              | 2       | 2       | 2       |          | 1       |      |

| Vdd [V]         | 1.5          | 1.8          | 1       | 1       | 1       | 1.15     | 1.1     | 2.2  |

| $P_{sat}$ [dBm] | 20.6         | 22.2         | 18.1    | 19.8    | 14      | 15.3     | 14.8    | 19.8 |

| $P_{1dB}$ [dBm] | 18.8         | 20.7         | 16.8    | 16      | 13.2    | 14.3     | 14.0    | 18.6 |

| $PAE_{max}$ [%] | $22.6^{(1)}$ | $21.3^{(1)}$ | 41.5    | 21      | 35.5    | 36.6     | 36.5    | 43.3 |

| $PAE_{1dB}$ [%] | $16.6^{(1)}$ | $14.6^{(1)}$ | 37.6    | 12.8    | 34.3    | 35.8     | 35.2    | 41.4 |

| $PAE_{max}$ [%] | $20^{(2)}$   | $19.6^{(2)}$ | 41.5    | 21      | 35.5    | 36.6     | 36.5    | 43.3 |

| $PAE_{1dB}$ [%] | $14.5^{(2)}$ | $13.5^{(2)}$ | 37.6    | 12.8    | 34.3    | 35.8     | 35.2    | 41.4 |

| Gain [dB]       | $33.1^{(3)}$ | $33.9^{(3)}$ | 20.5    | 22      | 15.7    | 16.3     | 10.0    | 13.6 |

| Area $[mm^2]$   | 0.144        |              | 0.361   | 0.59    | 0.16    |          | 0.28    |      |

<sup>(1)</sup>Not including PPA power consumption.

<sup>(2)</sup>Including PPA power consumption.

| Parameter       | This         |              | RFIC'17 | RFIC'17 | ISSC | ISSCC'16 |      | S'16 |

|-----------------|--------------|--------------|---------|---------|------|----------|------|------|

|                 | Work         |              | [3]     | [4]     | [5]  |          | [6]  |      |

| Tech. [nm]      | 28 SOI       |              | 28 Bulk | 28 Bulk | 28 I | 28 Bulk  |      | Bulk |

|                 | CM           | <b>IOS</b>   | CMOS    | CMOS    | CMOS |          | CMOS |      |

| Freq. [GHz]     | 2            | 6            | 27      | 32      | 30   |          | 28   |      |

| Pwr.Comb.       |              | 2            | 2       | 2       | ]    | l        | 1    |      |

| Gain Control    | 5 bits,      | 19dB         | None    | None    | No   | one      | None |      |

| No. of Stages   | 2            |              | 2       | 2       | 2    |          | 1    |      |

| Vdd [V]         | 1.5          | 1.8          | 1       | 1       | 1    | 1.15     | 1.1  | 2.2  |

| $P_{sat}$ [dBm] | 20.6         | 22.2         | 18.1    | 19.8    | 14   | 15.3     | 14.8 | 19.8 |

| $P_{1dB}$ [dBm] | 18.8         | 20.7         | 16.8    | 16      | 13.2 | 14.3     | 14.0 | 18.6 |

| $PAE_{max}$ [%] | $22.6^{(1)}$ | $21.3^{(1)}$ | 41.5    | 21      | 35.5 | 36.6     | 36.5 | 43.3 |

| $PAE_{1dB}$ [%] | $16.6^{(1)}$ | $14.6^{(1)}$ | 37.6    | 12.8    | 34.3 | 35.8     | 35.2 | 41.4 |

| $PAE_{max}$ [%] | $20^{(2)}$   | $19.6^{(2)}$ | 41.5    | 21      | 35.5 | 36.6     | 36.5 | 43.3 |

| $PAE_{1dB}$ [%] | $14.5^{(2)}$ | $13.5^{(2)}$ | 37.6    | 12.8    | 34.3 | 35.8     | 35.2 | 41.4 |

| Gain [dB]       | $33.1^{(3)}$ | $33.9^{(3)}$ | 20.5    | 22      | 15.7 | 16.3     | 10.0 | 13.6 |

| Area $[mm^2]$   | 0.144        |              | 0.361   | 0.59    | 0.16 |          | 0.28 |      |

<sup>(1)</sup>Not including PPA power consumption.

<sup>(2)</sup>Including PPA power consumption.

| Parameter       | This         |              | RFIC'17 | RFIC'17 | ISSC    | ISSCC'16 |         | 5'16 |

|-----------------|--------------|--------------|---------|---------|---------|----------|---------|------|

|                 | Work         |              | [3]     | [4]     | [5]     |          | [6]     |      |

| Tech. [nm]      | 28 SOI       |              | 28 Bulk | 28 Bulk | 28 Bulk |          | 28 Bulk |      |

|                 | CMOS         |              | CMOS    | CMOS    | CMOS    |          | CMOS    |      |

| Freq. [GHz]     | 2            | 6            | 27      | 32      | 30      |          | 28      |      |

| Pwr.Comb.       |              | 2            | 2       | 2       | ] ]     | 1        | 1       |      |

| Gain Control    | 5 bits,      | 19dB         | None    | None    | No      | one      | None    |      |

| No. of Stages   | 2            |              | 2       | 2       | 2       |          | 1       |      |

| Vdd [V]         | 1.5          | 1.8          | 1       | 1       | 1       | 1.15     | 1.1     | 2.2  |

| $P_{sat}$ [dBm] | 20.6         | 22.2         | 18.1    | 19.8    | 14      | 15.3     | 14.8    | 19.8 |

| $P_{1dB}$ [dBm] | 18.8         | 20.7         | 16.8    | 16      | 13.2    | 14.3     | 14.0    | 18.6 |

| $PAE_{max}$ [%] | $22.6^{(1)}$ | $21.3^{(1)}$ | 41.5    | 21      | 35.5    | 36.6     | 36.5    | 43.3 |

| $PAE_{1dB}$ [%] | $16.6^{(1)}$ | $14.6^{(1)}$ | 37.6    | 12.8    | 34.3    | 35.8     | 35.2    | 41.4 |

| $PAE_{max}$ [%] | $20^{(2)}$   | $19.6^{(2)}$ | 41.5    | 21      | 35.5    | 36.6     | 36.5    | 43.3 |

| $PAE_{1dB}$ [%] | $14.5^{(2)}$ | $13.5^{(2)}$ | 37.6    | 12.8    | 34.3    | 35.8     | 35.2    | 41.4 |

| Gain [dB]       | $33.1^{(3)}$ | $33.9^{(3)}$ | 20.5    | 22      | 15.7    | 16.3     | 10.0    | 13.6 |

| Area $[mm^2]$   | 0.144        |              | 0.361   | 0.59    | 0.16    |          | 0.28    |      |

$^{(1)}$ Not including PPA power consumption.

<sup>(2)</sup>Including PPA power consumption.

- demonstrated power amplifier for fully integrated 5G mmW system

- Implemented in 28 nm CMOS

- State of the art performance

- demonstrated power amplifier for fully integrated 5G mmW system

- Implemented in 28 nm CMOS

- State of the art performance

- Psat = 22.2 dBm

- demonstrated power amplifier for fully integrated 5G mmW system

- Implemented in 28 nm CMOS

- State of the art performance

- Psat = 22.2 dBm

- 1dB comp. = 20.7 dBm

- demonstrated power amplifier for fully integrated 5G mmW system

- Implemented in 28 nm CMOS

- State of the art performance

- Psat = 22.2 dBm

- 1dB comp. = 20.7 dBm

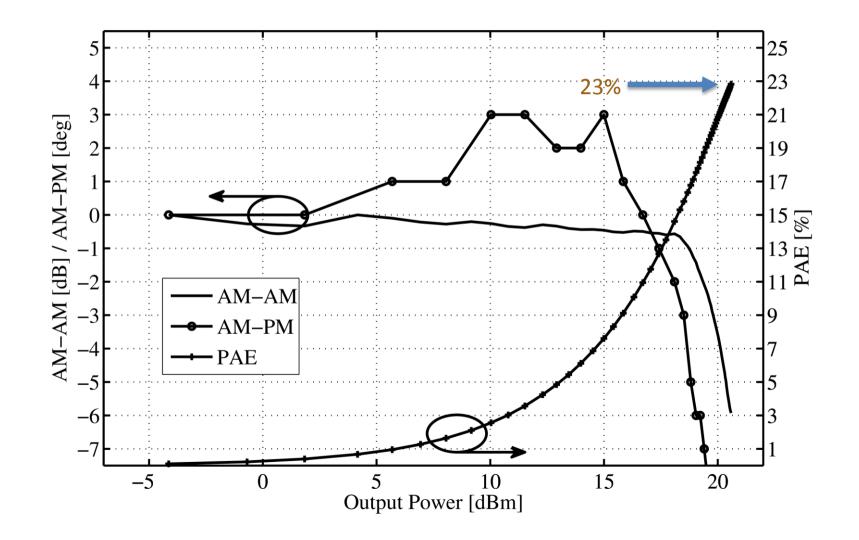

- AM-PM < 5 degrees below 1dB comp.</li>

- demonstrated power amplifier for fully integrated 5G mmW system

- Implemented in 28 nm CMOS

- State of the art performance

- Psat = 22.2 dBm

- 1dB comp. = 20.7 dBm

- AM-PM < 5 degrees below 1dB comp.</li>

- Smallest die area

# ERICSSON

## LUND UNIVERSITY